# 中国传媒大学 电子设计竞赛设计报告

题 目:基于 FPGA 简易数字信号传输性能分析仪

姓 名: 杨信

专 业: 电子信息工程

广播电视工程

指导教师 卢起斌 杜伟韬

# 摘要

设计一个简易数字信号传输性能分析仪,以两块含CycloneIII FPGA 芯片的DEO开发板为核心,由FPGA内部50MHz时钟通过P分频得到50kbps和100kbps数据率的数字信号和数据率10Mbps的伪随机信号(模拟信道噪声)。通过2阶有源巴特沃斯滤波器对数字信号进行滤波限带,然后叠加上幅度较小的伪随机序列(模拟信道噪声)。方案一:从FPGA内部直接引出时钟作为示波器同步信号显示眼图。方案二:对原信号进行曼彻斯特编码从滤波限带后的基带信号中运用数字锁相环直接提取时钟作为示波器同步信号显示眼图。本次设计中采用Verilog语言生成两个数字信号发生器和同步时钟,并用数字锁相环进行同步时钟提取。(各部分代码详情见附录)

关键词: FPGA Verilog 语言 有源巴特沃斯滤波器 曼彻斯特编码 数字锁相环 同步时钟 眼图

# 目录

- 一. 系统方案

- 1.1 数字信号发生器

- 1.2 滤波器设计模块

- 1.3 基带信号时钟提取

- 1.4 眼图显示

- 二. 电路设计及理论计算

- 2.1 数字信号发生器及曼彻斯特编码实现

- 2.2 有源滤波器设计及实现

- 2.3 基带信号时钟提取

- 2.4 眼图显示模块

- 三. 实物测试结果及数据

- 四. 问题思考(位同步时钟相位抖动)

#### 一. 系统方案

#### 系统框图

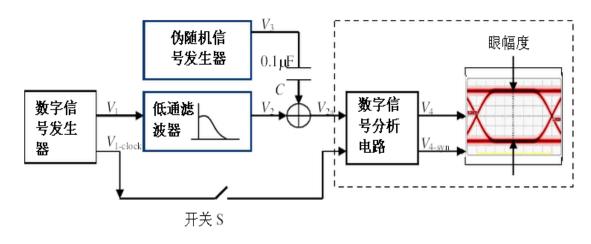

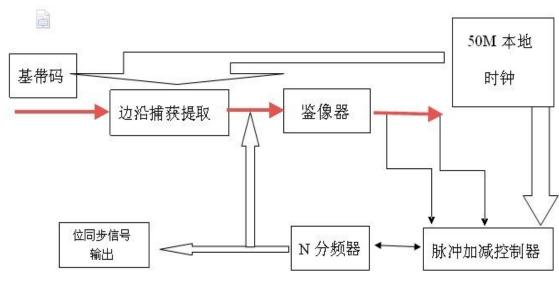

图 1 简易数字信号传输性能分析仪框图

本系统主要由两个 M 序列发生器模块,有源滤波器模块,基带信号同步时钟提取模块和眼图显示模块构成。

# 1.1 数字信号发生器

用分频器对 FPGA 内部 50M 时钟进行分频的到频率为 100K 占空比为 50%的时钟信号。每个时钟上升沿触发输出一个数据。得到我们需要的  $f(x)=1+x^2+x^3+x^4+x^8$  数据率为 100kbps 的 M 序列。采用 Verilog 对该逻辑进行硬件描述,具有体积小,重量轻,速度快,可靠性高等优点。

# 1.2 滤波器设计模块

本次设计选取选取巴特沃斯滤波器。它的特点是通频带内的频率响应曲线最大限度平坦,没有起伏,而在阻频带则逐渐下降为零。在振幅的对数对角频率的波特图上,从某一边界角频率开始,振幅随着

角频率的增加而逐步减少,趋向负无穷大。而且 2 阶有源巴特沃斯 滤波器可以达到衰减 40db/每十倍频程。

#### 1.3 基带信号时钟提取

本次设计采用 Verilog 编程利用 FPGA 运算速度快和内部资源丰富,进行同步信号的快速提取。对每个进入 FPGA 的基带信号的上升沿进行快速锁定从而获得位同步信号。

## 1.4 眼图显示

将滤波后的基带信号接入 TDS2022 示波器的 CH1,将时钟信号接入示波器的 CH2 并将 TRIGGER 中的信源触发方式选为 CH2。最后将 DISPLAY 中的持续时间选为 5 秒。这时就可以在示波器上看到清晰的眼图。

# 四. 电路设计及理论计算

# 2.1 数字信号发生器及曼彻斯特编码实现

对于数据率为 100kbps 的信号,由 FPGA 内部 50M 时钟进行 500 分频得到频率为 100K 占空比为 50%的时钟信号。每次时钟上升沿依次输出一个数据得到数据率为 100kbps 的信号。

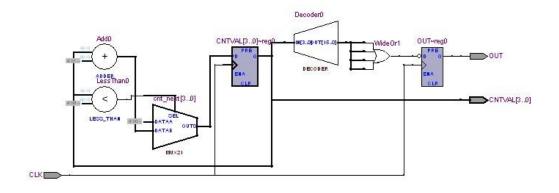

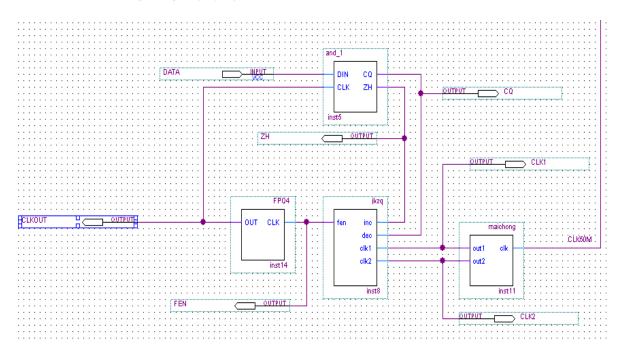

#### 上图为信号发生器 RTL 框图

另一个数据率为 10Mbps 的伪随机序列(模拟信道噪声)设计思路相同只需将 50M 时钟分频得到 10M 的时钟信号,每个时钟上升沿输出一个数据即可得到伪随机序列。

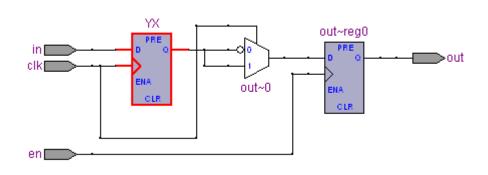

对于曼彻斯特编码,曼彻斯特编码的原理为若输入为 1 编码后输出为 10,若输入为 0 编码后输出为 01。因此设计 FPGA 编码器时,需要两个时钟一个频率为 100kHz 另一个频率为 200kHz。在频率为 100k 时钟上升沿采到数据后另一时钟作为使能。若采到数据为 1,使能为高时输出 1,使能为低时输出 0。若采到数据为 0,使能高时输出 0,使能低时输出 1。

### 编码器 RTL 框图

采用曼彻斯特编码的好处是编码后 0—1 跳变增多易于后续数字 锁相环对位同步时钟的提取。

#### 2.2 有源滤波器设计及实现

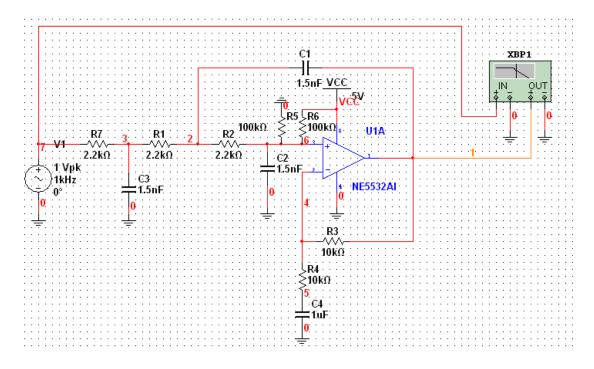

滤波器要求截止频率为100kHz 带外衰减为40dB/十倍频程。从滤波器阶数可分为一阶和高阶,阶数越高,幅频特性越陡峭。高阶滤波通常可由一阶和二阶滤波器级联而成。采用集成运放构成的 RC 有源滤波器具有输入阻抗高,输出阻抗低,可提供一定增益,截止频率可调等特点。

设计要求的截止频率较高,因此要求运放的增益带宽较宽,选用通频带较宽的运放,本设计选用运放 NE5532,带宽为10MHz,可以满足100kHz 截止频率的设计要求。

本次设计采用二阶有源巴特沃斯滤波器传递函数为:

$$|A(jw)| = \frac{A_0}{\sqrt{1 + (w/w_c)^{2n}}}$$

为了设计方便本次设计中选取  $R_1 = R_2 = R$   $C_1 = C_2 = C$

$$f_0 = f_c = \frac{1}{2\pi RC}$$

实际电路板焊接调试后选用 R = 2.2KΩ C = 1.5nF 可以并在前端再加一级 RC 低通滤波基本节可以达到设计要求的指标

下图为实际焊接的电路图

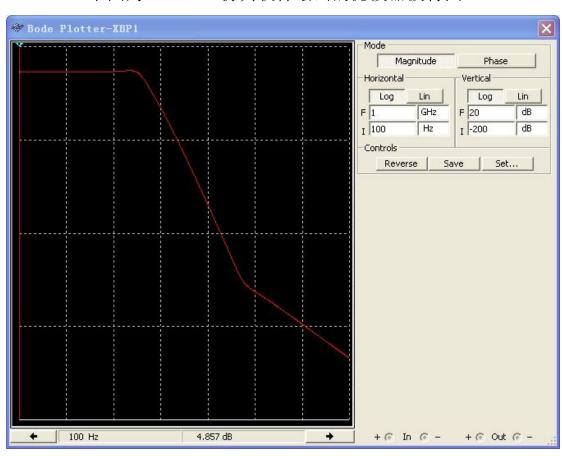

下图为 multisim 仿真软件绘出的滤波器波特图

带内增益为 4.8db

100kHz 为 0.1db 1MHz 为-54db 满足设计要求衰减 40db/十倍频程

#### 2.3 基带信号时钟提取

位同步提取模块主要由边沿捕获器、鉴相器、脉冲加减控制器和N分频器四个部分组成。输入的非归零二进制码元经过边沿提取后送入鉴相器,鉴相器对码元上升沿的相位与位同步提取后输出信号上升的相位进行比较,当位同步提取输出信号的相位超前时输出一个减脉冲信号,滞后时输出一个加脉冲信号,然后送入脉冲加减控制器,脉冲加减控制器根据鉴相器的输出信号来控制相位的加减。最后使位同步信号维持在一个动态平衡,输入信号的上升沿和位同步信号上升沿对齐。

本设计提取的同步时钟的最大相位误差为 360/N 度, N 值的大小由编程设定,N 值取的越大则相位误差越小,但 N 越大则达到同步锁定的速度就越慢。我们应当兼顾速度和精度来适当的选取 N 的值。

本次设计中 N = 25M/100K =250

此图为位同步时钟提取框图

## 基于 FPGA 最终设计结果

各模块详细代码请见附录

# 2.4 眼图显示模块

将滤波后的基带信号接入 TDS2022 示波器的 CH1,将时钟信号接入示波器的 CH2 并将 TRIGGER 中的信源触发方式选为 CH2。最后将 DISPLAY 中的持续时间选为 5 秒。这时就可以在示波器上看到清晰的眼图。参照以上步骤即可在在示波器上显示清晰的眼图

# 三. 实物测试结果及数据

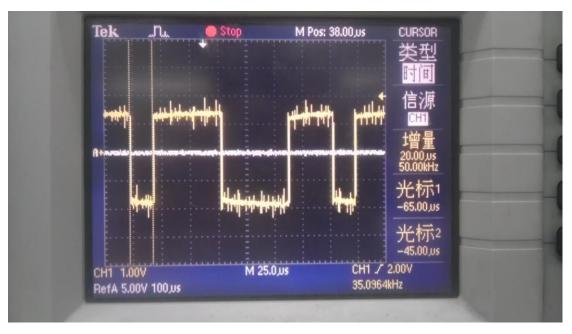

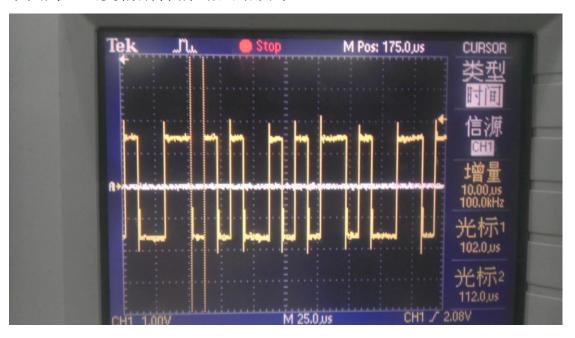

在示波器上可以看出输出序列为:

101110001 之后继续输出 101110001 满足设计要求的序列数据率 为 50kbps。

下图为经过曼彻斯特编码后的序列: 1->10 0->01

10 01 10 10 10 01 01 01 10

编码后数据率为100kbps,示波器上显示的编码结果与计算一致。

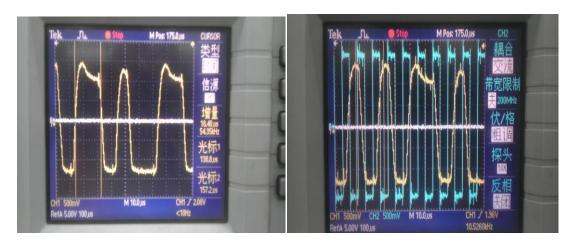

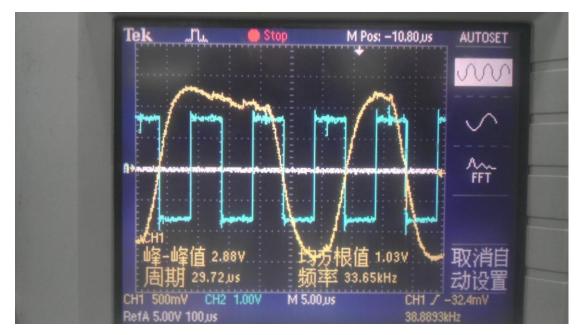

此图为数据率为 100kbps 的信号通过截止频率为 100kHz 40db/每十倍频程有源滤波器后的滤波限带的基带信号。从图中明显可以发现滤波后信号变的不规则出现了波形失真,如果不进行抽样判决很容易发生误码。

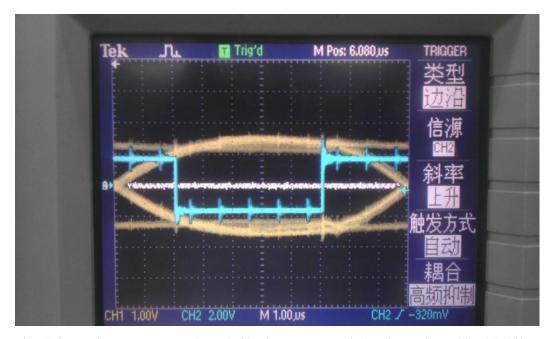

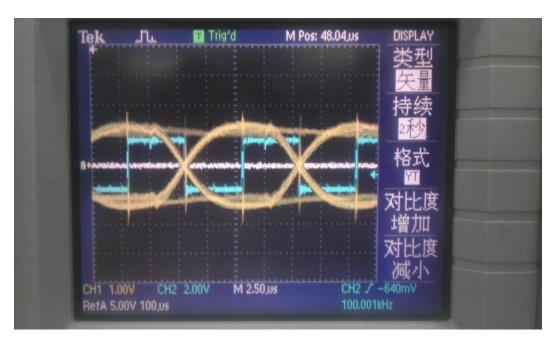

此图为方式一显示眼图 直接将 FPGA 内部生成序列的时钟信号接入示波器的 CH2 并将 TRIGGER 中的信源触发方式选为 CH2。显示出完整的眼图。

此图为叠加上 1Mbps 伪随机序列(模拟信道噪声)后的眼图, 从图中可以看出伪随机序列对眼图的质量产生的很大的影响。噪声容 限减小,噪声越大,线条越粗,越模糊,眼睛张开得越小。

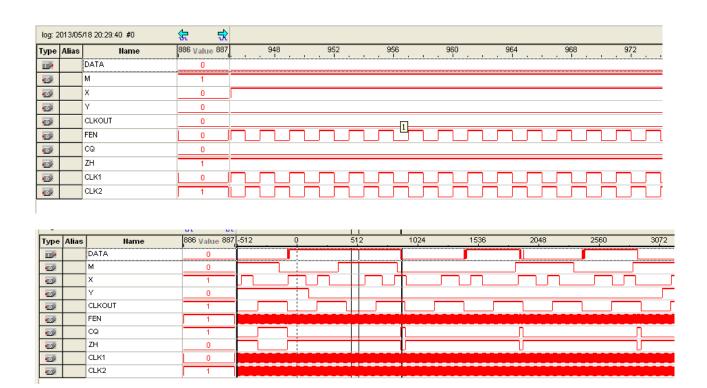

此图中蓝色周期信号为数字锁像环恢复的位同步信号,在图中可以看到位同步信号与时钟沿对沿对齐。原本意图是想上升沿对齐可示 波器上看到的却是下降沿对齐,这地方还没想明白。

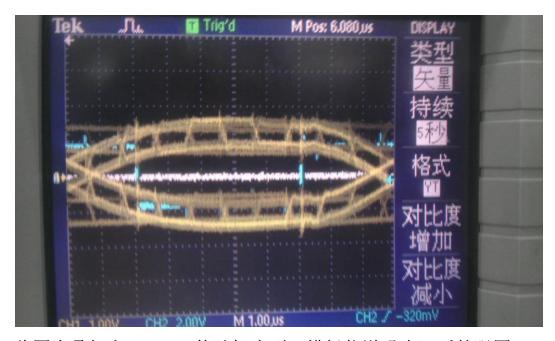

此图为方式二显示眼图 将滤波限带后基带信号送入第二块 FPGA 板内部用数字锁相环恢复位的同步时钟信号接入示波器的 CH2 并将 TRIGGER 中的信源触发方式选为 CH2。显示出的眼图与位同步信号。

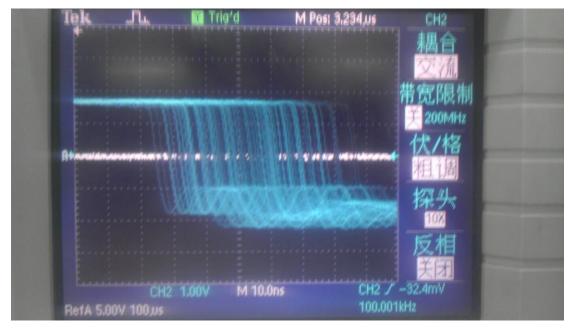

# 五. 问题思考(位同步时钟相位抖动)

上图为将示波器 sec/div 调为 10ns 时对数字锁像环恢复的位同步时钟下降沿进行的观察。可以发现恢复的位同步信号的相位抖动还是十分严重的。步时钟的最大相位误差为 360/N 度,N 值的大小由编程设定,N 值取的越大则相位误差越小,但 N 越大则达到同步锁定的速度就越慢。我们应当兼顾速度和精度来适当的选取 N 的值。本次设计中 N=25M/100K=250。

上图为 signaltap 中抓取的实时信号可以发现 CQ (相位超前) ZH (相位滞后) 在不停的改变对相位进行加减从而对基带信号的上升沿进行跟踪,因此会发生相位抖动。 跟踪后使恢复的时钟信号维持在一个动态的平衡。